# **Project Essentials**

### Summary

Application Note AP0129 (v1.1) Nov 15, 2005 The basis of every design captured in Altium Designer is the project. This application note outlines the different kinds of projects, techniques for working on projects and how to use the Projects panel effectively.

### What is an Altium Designer Project?

The starting point for every design created in Altium Designer is a project. An Altium Designer project is a set of design documents whose output defines a single implementation. For example, the schematics and PCB in a PCB project output the fileset required to manufacture a single printed circuit board, while the schematics and HDL in an FPGA project output the fileset required to program a single FPGA.

## **Types of Projects**

Altium Designer supports a number of different kinds of projects. Below is a brief description of each.

### PCB Project (\*.PrjPcb)

#### The set of design documents required to manufacture a printed circuit board.

The electronic circuit is captured as a schematic, built up from libraries of component symbols which are placed and wired together. The design is transferred to the PCB editor where each component is instantiated as a footprint (pattern) and the circuit wiring becomes point-to-point connection lines. A shape for the final PCB is defined, along with the physical layers the board will include. Design rules specify the layout requirements, such as routing widths and clearance. The components are positioned within the board shape and the connection lines are then replaced by routing, either manually or automatically. When the design is complete, standard format output files are generated which can be used to fabricate the blank board, configure an assembly machine, and so on.

### FPGA Project (\*.PrjFpg)

# The set of design documents that can be processed to program a Field Programmable Gate Array.

The design is captured using schematics and/or HDL code (VHDL or Verilog). Constraint files are added to the project to specify design requirements such as the target device, internal net-to-device pin mapping, net frequency requirements, clock pin allocations, and so on. Design synthesis translates the source data into a low-level gate form, in a standard file format known as EDIF. Device vendor tools then process the EDIF data and attempt to place and route the design in such a way that it will fit in the

#### **Project Essentials**

specified target device, producing a device program file if successful. The design can then be implemented in the target device fitted to a suitable development board and the design can be tested.

### Embedded Project (\*.PrjEmb)

# The set of design documents required to produce a software application that can be embedded with its executing processor in an electronic product.

The source of the design is captured in C and/or assembly language. When coding is complete, all source files are compiled into assembly language. The assembler then converts them into machine language (object code). The object files are then linked together and mapped into the specified memory space, producing a single, target-ready output file.

### Core Project (\*.PrjCor)

# The set of design documents required to produce an EDIF representation (model) of a functional component that can be implemented in an FPGA.

The design is captured using schematics and/or HDL code (VHDL or Verilog). Constraint files are added to the project to specify the supported target device(s). Design synthesis translates the source data into a low-level gate form, in a standard file format known as EDIF. A component symbol is drawn to represent the component on a schematic sheet, which then references its EDIF description.

### Integrated Library (\*.LibPkg) & (\*.IntLib)

#### The set of design documents required to produce an integrated library.

Schematic symbols are drawn in a library editor, and model references defined. Referenced models can include PCB footprints, circuit simulation models, signal integrity models and three-dimensional mechanical models. Files that contain the models are added to the Integrated Library Package (\*.LibPkg), or search paths are defined to identify their location. The source schematic symbol libraries and required models are then compiled into a single file, referred to as an Integrated Library.

### Script Project (\*.PrjScr)

#### A set of design documents that stores one or more Altium Designer scripts.

A set of instructions that are interpreted whenever a script is executed in Altium Designer. The scripts are written and debugged in the same environment. There are two types of scripts - *script units* and *script forms*. A Script unit can use the DXP Application Programming Interface (API) to modify design objects on a design document. A script form hosts controls, as well as using the DXP API to a provide script dialog that act on design documents open in Altium Designer.

## The Role of the Project File

The set of design documents that make up the project are bought together by the project file. The project file stores all project-relevant settings, including a link to each document in the project, and all project-relevant options. Each document in the project is stored as a separate file, which is linked to the project via a relative reference for files on the same logical drive, or an absolute reference for files on a different logical drive. Outputs generated from the project are also referenced in the project file.

The exact set of project options stored will depend on the project type. It will include those options configured in the *Options for Project* dialog, such as:

- Compiler error check settings

- Design synchronization settings

- Design compiling settings

- Location of output files

- Multi-channel annotation settings

Other project settings stored in the project file include:

- Schematic annotation settings

- Output settings such as reports, print, Gerber, and so on. Note that these are the output settings accessed via the schematic or PCB editor menus, not the output settings defined in an OutJob document.

## **The Projects Panel**

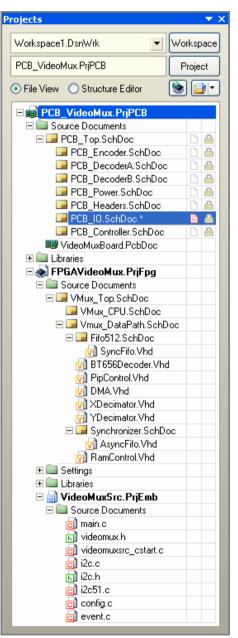

The panel that is perhaps the most often used in Altium Designer is the **Projects** panel. The **Projects** panel is your view into the project. When you open a project its documents are displayed, as shown in Figure 1.

As well as allowing multiple documents to be open for editing, the environment also supports multiple projects being open at the same time. These could be unrelated projects, or they could be related projects, as shown in Figure 1. In the figure there are three related projects – a PCB project which includes an FPGA on it, the project for that FPGA which includes a soft-core processor, and an embedded project for the software that runs on the softcore processor inside the FPGA.

Figure 1. Three related projects open in the Projects panel.

### **Making Changes to the Project**

The document that you are currently editing, referred to as the *active* document, is highlighted in the panel. You will notice in Figure 1 that the project as well as the active document being highlighted, so is the *active* project. Any change made via a command in the **Projects** menu will be made to the active project.

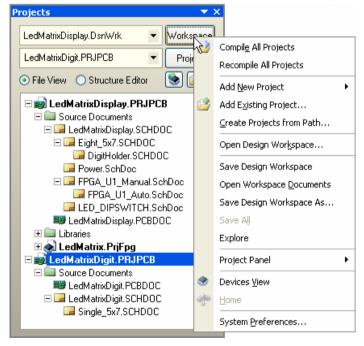

When you have multiple projects open for editing, a simple way to perform project related commands on the project of your choice is to right-click on the project name in the **Projects** panel. When you do, a context sensitive menu will appear, where you can perform project actions regardless of whether the active document belongs to that project or not. Figure 2 shows that a document in the embedded project is active, but the PCB project has been right-clicked on to display the context sensitive project menu.

Figure 2. Right-click on the project name to access a set of project-related commands.

### **Project Panel Display Options**

There are a number of display options for the **Projects** panel. The default display mode is to show project documents grouped into separate display folders, such as Source Documents, Libraries, Settings, and so on. There are a number of other display modes for project document grouping, as well as grid display, mouse click behavior, how the project folders present when a project is opened, and so on.

These options are configured in the **Projects Panel** page in the **System** section of the *Preferences* dialog (**DXP**)

| Project                                                                                                          |                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Categories<br>General<br>File View<br>Structure View<br>Sorting<br>Grouping<br>Default Expansion<br>Single Click | General<br>✓ Show open/ modified status<br>✓ Show VCS status<br>Show document position in project<br>✓ Show full path information in hint<br>✓ Show Grid |

|                                                                                                                  |                                                                                                                                                          |

Figure 3. Controlling the presentation in the Projects panel

menu). A quick way to access these Project panel settings is to click the **b** button at the top of the panel, as shown in Figure 3.

Note that the folders shown in the **Projects** panel do not represent folders on the hard drive. They are provided to help present the project documents in a manageable way.

### **Order of Documents in a Project**

Documents within a group, such as Source Documents, are displayed by default in the order that they were added to the project (which is the order they are listed in the project file). To change the order of documents within a display folder, click, drag and drop a document to its new location. Once a project has been compiled, the source documents are also displayed showing the hierarchy of the design.

Note that you cannot build project hierarchy by dragging documents in the panel. The parent-child hierarchical relationship between documents in a project is defined by the sheet symbol to sub-sheet definitions. For more information about project hierarchy, refer to the *Connectivity and Multi-Sheet Design* article.

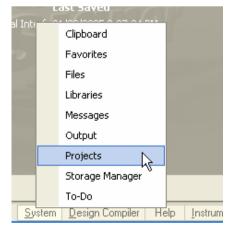

### **Displaying the projects panel**

If the **Projects** panel is not currently visible, you can open it by clicking the System button at the bottom right of the workspace, and selecting **Projects** from the menu that appears, as shown in Figure 4.

Figure 4. Controlling panel visibility

## **Creating a Project**

| DX | <u>(</u> P [ | File | ⊻iew                           | F <u>a</u> vorites | Proje <u>c</u> t                       | W | indow               | <u>H</u> elp                |     | _        |                     |     |

|----|--------------|------|--------------------------------|--------------------|----------------------------------------|---|---------------------|-----------------------------|-----|----------|---------------------|-----|

|    | 3            |      | New                            |                    |                                        | • |                     | <u>S</u> chematic           |     |          |                     |     |

|    |              | 2    | Open                           |                    | Ctrl+O                                 |   | 疁                   | <u>Р</u> СВ                 |     |          |                     |     |

|    |              |      | ⊆lose                          |                    | Ctrl+F4                                |   | Ø                   | VHDL Document               |     |          | _                   |     |

|    | 6            | 1    | Open Pr                        | oject              |                                        |   | V                   | Verilog Document            |     |          |                     |     |

|    |              |      | Open Design Wor <u>k</u> space |                    |                                        |   | C                   | $\subseteq$ Source Document |     |          |                     |     |

|    | Ь            |      | Save Project Save Project As   |                    |                                        |   | ß                   | C <u>H</u> eader Document   |     |          |                     |     |

|    | ٢            |      |                                |                    |                                        | A | ASM Source Document |                             |     |          |                     |     |

|    |              |      |                                | sign Worksp        | Dace                                   |   |                     | Text Document               |     |          |                     |     |

|    |              |      | Save De                        | sign Worksp        | oace As                                |   | 3                   | CAM Document                |     |          |                     |     |

|    |              |      | Save Al                        |                    |                                        |   | <u>e</u>            | Outp <u>u</u> t Job File    |     |          |                     |     |

|    | 2            |      | Protel 9                       | 9 SE Import        | Wizard                                 |   | •                   | Database Lin <u>k</u> File  |     |          |                     |     |

|    | -            |      |                                | Documents          |                                        |   |                     | Project                     | ×   | <b>B</b> | PC <u>B</u> Project |     |

|    |              |      | Recent l                       |                    |                                        | Ĺ |                     | Library                     | ۲   | ۲        | EPGA Project        |     |

|    |              |      |                                | Workspaces         |                                        | Ĺ |                     | Script Files                | ۲   |          | Core Project        | N   |

|    |              |      | ·                              |                    | $Mi\underline{x}ed$ -Signal Simulation | ۲ | Þ                   | Integrated Libr             | ary |          |                     |     |

|    |              |      | E <u>x</u> it                  |                    | Alt+F4                                 |   |                     | <u>O</u> ther               | ۲   | <b>a</b> | Embedded Proj       | ect |

|    |              |      |                                |                    |                                        |   | h                   | Design Workspace            |     | 5        | Script Project      |     |

Use the options in the **File** » **New** » **Project** submenu to create a new project, as shown in Figure 5.

Note that the project file only exists in memory when first created, use the **Save** or **Save As** commands to save it with a suitable name in the required location.

FPGA, Core and Embedded project filenames should not include any spaces.

Figure 5. Drill down from the File menu to create a new project.

## Adding and Removing Documents from a Project

Once you have created the project and saved it to the required location, you are ready to start adding the design documents. The easiest way to add new or existing design documents to a project is to right-click on the project name in the **Projects** panel and use the **Add New to Project** or **Add Existing to Project** menu options.

You can also add other project-relevant documents to your project, such as Word® files or Adobe® PDFs. Add them in the usual way, you will need set the **File Type** list in the *Choose Document to Add* dialog to All Files (\*.\*) to see the files.

Figure 6. include other types of documents in your project.

### **Setting Project Options**

Project settings are configured in the *Options for Project* dialog. You can access this from the **Projects** menu on the main menubar, or by right-clicking on the project name in the **Projects** panel.

| rror Reporting Connection Matrix Class Generation Comparator ECO Generation Optio | ons Multi-Channel Default Prints Search Paths Parameter |

|-----------------------------------------------------------------------------------|---------------------------------------------------------|

| /iolation Type Description                                                        | A Report Mode                                           |

| Violations Associated with Buses                                                  |                                                         |

| Bus indices out of range                                                          | 🦲 Warning                                               |

| Bus range syntax errors                                                           | Error                                                   |

| Illegal bus definitions                                                           | 🚞 Error                                                 |

| Illegal bus range values                                                          | Error                                                   |

| Mismatched bus label ordering                                                     | 🗀 Warning                                               |

| Mismatched bus widths                                                             | 🛄 Warning                                               |

| Mismatched Bus-Section index ordering                                             | 🦲 Warning                                               |

| Mismatched Bus/Wire object on Wire/Bus                                            | 🚞 Error                                                 |

| Mismatched electrical types on bus                                                | 🗀 Warning                                               |

| Mismatched Generics on bus (First Index)                                          | 🦲 Warning                                               |

| Mismatched Generics on bus (Second Index)                                         | 🗀 Warning                                               |

| Mixed generic and numeric bus labeling                                            | 🗀 Warning                                               |

| Violations Associated with Components                                             |                                                         |

| Component Implementations with duplicate pins usage                               | 🗀 Warning                                               |

| Component Implementations with invalid pin mappings                               | Error                                                   |

| Component Implementations with missing pins in sequence                           | 🛄 Warning                                               |

| Components containg duplicate sub-parts                                           | Error                                                   |

| Components with duplicate Implementations                                         | 🦲 Warning                                               |

| Components with duplicate pins                                                    | 🗀 Warning                                               |

| Duplicate Component Models                                                        | 🔁 Warning                                               |

| Duplicate Part Designators                                                        | Error                                                   |

| Errors in Component Model Parameters                                              | Error                                                   |

| Extra pin found in component display mode                                         | 🛄 Warning                                               |

| Mismatched hidden pin connections                                                 | Error                                                   |

| Mismatched pin visibility                                                         | Error                                                   |

| Missing Component Model Parameters                                                | Error                                                   |

Below are references to other documents in the Altium Designer Documentation Library that talk more about setting project options. You can also use **F1** and **What's This** help in the *Options for Project* dialog for more details.

- For PCB project options, see the *Getting Started with PCB Design* tutorial.

- For FPGA project options, see the Getting Started with FPGA Design tutorial.

- For Core project options, refer to the Creating a Core Component tutorial.

- For embedded projects, the Using the Embedded Tools guide for the relevant processor includes a topic on Setting the Embedded Project Options.

For the TSK3000, refer to Using the TSK3000 Embedded Tools.

For the TSK51x/TSK52x, refer to Using the TSK51x TSK52x Embedded Tools.

For the TSK165x, refer to Using the TSK165x Embedded Tools.

For the TSK80x, refer to Using the TSK80x Embedded Tools.

### **Managing Project Documents**

It is important to appreciate that the presentation of documents in the **Projects** panel does not reflect how they are stored on the hard drive. One way to think of it is that the **Projects** panel presents a logical representation of the project. The organization of the document storage is up to you – you might have project documents stored on a common company server, with your own idea or scratch-pad files stored on your own PC. Or you might use Altium Designer with a version control system, checking project documents out from the central repository into your personal workspace on a server.

#### **Sharing Documents Between Projects**

Because each project document is linked to the project you can share documents between multiple projects. It might be a schematic sheet for a standard power supply you use across different products, or it might be a section of the design that you would like to simulated separately.

#### Saving Project Documents with a New Name

There are **Save As** commands that allow you to save a document with a new name. Note that this is not a rename process, after doing this you will have both the old document and the new document on the hard drive. Performing a **Save As** on a document will also update the project – done to ensure that the document remains a part of the project. If you want to create a back-up copy of a document without affecting the project, use the **Save Copy As** command.

If a document that belongs to two projects is saved with a new name and both projects are open when you do this, then both projects will be updated to reflect the name change, maintaining the integrity of both of the projects.

Note that you cannot relocate a project by performing a **Save As** action on the Project document itself and saving it to a new location – this will only save the project document to that location. It will also update all the links to the documents that are in the project, linking from the new project document to the old location where the actual project documents are stored! Again, the **Projects** panel is not for file management, in this case you must relocate the project and its documents via the operating system.

| Storage Manager            |                       |           |             |                     |      |             |                 |                       |                       | <b>•</b> × |

|----------------------------|-----------------------|-----------|-------------|---------------------|------|-------------|-----------------|-----------------------|-----------------------|------------|

| Folders                    |                       |           |             |                     |      | Files       |                 |                       |                       | ^          |

| Folders                    | File                  |           |             | Size                | Kind | Δ           | Date Modified   |                       | Status                |            |

| 🖃 📷 PCB_VideoMux.PrjPCB    | 时 VideoMuxBoar        | rd.PcbDoc |             | 1,335,808           |      | PCB         | 13/12/2004 1    | 2:35:52 PM            | Version control disab | led 🔜      |

| 🕂 🦳 src                    | PCB_Footprint         | s.PcbLib  |             | 112,128             |      | PCBLIB      | 12/01/2004      | 5:48:06 PM            | Version control disab | led        |

|                            | PCB_VideoMu           | ix.PrjPCB |             | 16,189              |      | PobProject  | 9/06/2004       | 2:47:18 PM            | Version control disab | led        |

|                            | PCB_Controlle         | r.SchDoc  |             | 445 440             |      | SCH         | 22/11/2004      | 5:35:12 PM            | Version control disab | led        |

|                            | 📴 PCB_DecoderA.SchDor |           |             |                     |      | SCH         | 22/11/2004      | 5:35:04 PM            | Version control disab | led        |

| 📴 PCB_DecoderB.Schl        |                       |           | oderB.SchDo |                     |      | SCH         | 22/11/2004      | 5:35:06 PM            | Version control disab | led        |

|                            | 🕞 PCB_Encoder.SchDoc  |           | Rename N    |                     |      | SCH         | 22/11/2004      | 5:35:02 PM            | Version control disab | led        |

|                            | rs.SchDoc             |           |             |                     | SCH  | 22/11/2004  | 5:35:08 PM      | Version control disab | led 🤍                 |            |

| C:\Program Files\Altium200 |                       |           |             | fresh               | ce   | e Designs\\ | /ideoMultiplexe | r\PCB_Cont            | roller.SchDoc         |            |

| VCS Revisions              |                       |           |             | Copy Local History  |      |             |                 |                       |                       |            |

| Revision Time              | Username              | Commen    | Paste       |                     |      | Time        |                 |                       |                       |            |

|                            |                       |           | Pu          | rge <u>H</u> istory | C    | ontents     |                 | 22/11/2004            | 5:35:12 PM            |            |

|                            |                       |           |             |                     |      |             |                 |                       |                       |            |

### Using the Storage Manager to Manage Project Documents

Figure 7. Use the Storage Manager to rename and delete project documents.

Where the **Projects** panel presents the logic structure of the project, the **Storage Manager** provides you with a file management type interface. It lists the documents in the active project, displaying the path to the selected document below the list of documents. Right-click on a document name to perform file management tasks such as renaming or deleting, as shown in Figure 7.

**IF** For more information on the **Storage Manager**, press **F1** when the cursor is over the panel.

For more information on interfacing to a version control system refer to the *Working with a Version Control System* tutorial.

### **Grouping Related Projects – the Design Workspace**

Often you will have projects that are related, perhaps for a product that includes multiple PCBs, or perhaps you like to group the various revisions of a board design together. You can group related projects by creating a Design Workspace.

You can think of a Workspace as a set of projects. The **Projects** panel actually displays the current Workspace – either the default one, or one you have created or opened.

To save the currently opened set of projects as a Workspace click the **Workspace** button at the top of the **Projects** panel, or use the commands in the **File** menu.

When you open a different Workspace the current Workspace must first be closed, you will be prompted to save any unsaved documents, projects or changes to the current Workspace first.

Figure 8. Save a set of related projects as a Design Workspace.

### **Revision History**

| Date        | Version No. | Revision                               |  |  |  |  |

|-------------|-------------|----------------------------------------|--|--|--|--|

| 08-Apr-2005 | 1.0         | New document release                   |  |  |  |  |

| 15-Nov-2005 | 1.1         | Reviewed for Altium Designer 6 release |  |  |  |  |

Software, documentation and related materials:

Copyright © 2005 Altium Limited.

All rights reserved. You are permitted to print this document provided that (1) the use of such is for personal use only and will not be copied or posted on any network computer or broadcast in any media, and (2) no modifications of the document is made. Unauthorized duplication, in whole or part, of this document by any means, mechanical or electronic, including translation into another language, except for brief excerpts in published reviews, is prohibited without the express written permission of Altium Limited. Unauthorized duplication of this work may also be prohibited by local statute. Violators may be subject to both criminal and civil penalties, including fines and/or imprisonment. Altium, Altium Designer, CAMtastic, CircuitStudio, Design Explorer, DXP, LiveDesign, NanoBoard, NanoTalk, Nexar, nVisage, P-CAD, Protel, Situs, TASKING, and Topological Autorouting and their respective logos are trademarks or registered trademarks of Altium Limited or its subsidiaries. All other registered or unregistered trademarks referenced herein are the property of their respective owners and no trademark rights to the same are claimed.